# **MINICURSOS**

# XXIERAD

ESCOLA REGIONAL DE ALTO DESEMPENHO DA REGIÃO SUL

Fomento:

Patrocínio Diamante:

NEC

Patrocínio Prata: **Unisociesc**

Realização:

Organização:

## ANDREA CHARÃO MATHEUS S. SERPA

# MINICURSOS DA XXI ESCOLA REGIONAL DE ALTO DESEMPENHO DA REGIÃO SUL (ERAD/RS)

Porto Alegre

Sociedade Brasileira de Computação – SBC

2021

#### Dados Internacionais de Catalogação na Publicação (CIP)

E74 Escola Regional de Alto Desempenho da Região Sul (21. : 2021 : Joinville, SC)

Minicursos da XXI Escola Regional de Alto Desempenho da Região Sul [recurso eletrônico] / Organizadores: Andrea Charão, Matheus Serpa. – Porto Alegre: SBC, 2021.

ISBN 978-65-87003-50-4

1. Computação – Evento. 2. Processamento de alto desempenho. I. Charão, Andrea. II. Serpa, Matheus. III. Universidade Federal de Santa Maria. IV. Universidade Federal do Rio Grande do Sul. V. Universidade do Estado de Santa Catarina. VI. Título.

CDU 004 (059)

Catalogação elaborada por Francine Conde Cabral CRB-10/2606

#### **ERAD/RS 2021**

#### XXI Escola Regional de Alto Desempenho da Região Sul

14 a 16 de abril de 2021 Evento Online

http://labp2d.joinville.udesc.br/erad2021/

A XXI Escola Regional de Alto Desempenho da Região Sul (ERAD/RS 2021) foi planejada para ser uma edição histórica para a comunidade de Computação de Alto Desempenho (CAD) da Região Sul do Brasil, pois a escola romperia as fronteiras do Rio Grande do Sul pela primeira vez desde a sua criação. A cidade escolhida foi Joinville, no estado de Santa Catarina, que acolheria os pesquisadores no campus da Universidade do Estado de Santa Catarina (UDESC) entre os dias 14 e 16 de abril de 2021. Todavia, devido a pandemia de COVID-19, não foi possível realizar um evento presencial. Portanto, o evento ocorreu de forma online e com transmissão gratuita para toda a comunidade através do Youtube da ERAD/RS.

A ERAD/RS é promovida anualmente pela Sociedade Brasileira de Computação (SBC) e pela Comissão Regional de Alto Desempenho da Região Sul (CRAD/RS). O público alvo da escola são alunos, profissionais e professores/pesquisadores que atuam direta ou indiretamente na área de Computação de Alto Desempenho (CAD) e em áreas correlatas. O evento engloba a região sul do Brasil (RS, SC e PR). Os principais objetivos da escola são:

- Qualificar os profissionais do sul do Brasil nas áreas que compõem o processamento de alto desempenho;

- Prover um fórum regular onde possam ser apresentados os avanços recentes nessas áreas;

- Discutir formas de ensino de processamento de alto desempenho nas universidades.

A programação da ERAD/RS 2021 foi composta por sessões técnicas com apresentações de 50 trabalhos nos fóruns de Iniciação Científica (IC) e de Pós-Graduação (PG). Além disso, o evento proporcionou aos participantes 3 palestras científicas, 5 palestras empresariais, 7 minicursos e uma maratona de programação paralela. Ainda, com intuito de incentivar a participação de mulheres na área de CAD, o evento abriu espaço para um workshop e roda de conversa sobre mulheres na área de CAD, promovido pelo Women in HPC (WHPC).

A edição de 2021 da escola foi coordenada pelos professores Maurício Aronne Pillon (UDESC), Márcio Castro (UFSC) e Claudio Schepke (UNIPAMPA). O fórum de IC foi coordenado pelos professores Odorico Mendizabal (UFSC) e Marco A. Zanatta Alves (UFPR). O fórum de PG foi coordenado pelos professores Guilherme P. Koslovski (UDESC) e Tiago Ferreto (PUCRS). Os minicursos foram coordenados pela professora Andrea Charão (UFSM) e pelo doutorando Matheus Serpa (UFRGS). A maratona de programação paralela foi coordenada pelos professores Dalvan Griebler (PUCRS/SETREM) e João Vicente F. Lima (UFSM). A equipe organizadora local foi coordenada pelos professores Charles Christian Miers (UDESC) e Ricardo Pfitscher (UFRGS/UNISOCIESC).

# Índice

| Mensagem da Coordenação Geral          | ii |

|----------------------------------------|----|

| Mensagem da Coordenação dos Minicursos | iv |

| Comitês Organizadores                  | V  |

| Minicursos                             | V  |

#### Mensagem da Coordenação Geral

É com imenso prazer e entusiasmo que saudamos e damos as boas vindas à vigésima primeira edição da Escola Regional de Alto Desempenho da Região Sul (ERAD/RS 2021), que neste ano aconteceu de forma virtual entre os dias 14 e 16 de abril de 2021. A ERAD/RS é um evento anual, promovido pela Sociedade Brasileira de Computação (SBC), por meio da Comissão Regional de Alto Desempenho da Região Sul (CRAD/RS), desde 2001.

Coordenar e organizar um evento da magnitude da ERAD/RS é, por si só, um grande desafio. Trazêlo, pela primeira vez na história do evento, para fora do Estado do Rio Grande do Sul, fez com que nossa responsabilidade aumentasse ainda mais. Por fim, organizá-lo e executá-lo em meio a uma pandemia ampliou ainda mais os riscos e as preocupações envolvidas em todo o processo.

É inegável que a impossibilidade imposta pela pandemia de realizarmos a primeira ERAD/RS fora do estado do Rio Grande do Sul nos gerou certa frustração. Afinal, gostaríamos de ter acolhido os estudantes e pesquisadores da área de Computação de Alto Desempenho (CAD) em Joinville, a cidade mais populosa do estado de Santa Catarina. Porém, durante a organização do evento, nós coordenadores não medimos esforços para fazer um evento virtual de qualidade dentro das limitações impostas pela crise na saúde que afetou a vida de todos nós.

Neste ano, a ERAD/RS contou com fomento governamental da FAPESC, além do patrocínio na categoria diamante das empresas NEC, LANIAQ e de uma parceria conjunta entre DELL e NVIDIA. Ainda, o evento foi patrocinado pela SDC (patrocínio ouro) e pela UNISOCIESC (patrocínio prata).

Agradecemos, em especial, a todos os(as) autores(as) que submeteram seus trabalhos às sessões técnicas, às empresas patrocinadoras e aos diversos convidados que aceitaram prontamente nosso convite e, sem dúvida alguma, engrandeceram a ERAD/RS com as suas participações.

Por fim, agradecemos todos os coordenadores dos eventos da ERAD/RS, que tomaram para si diversos encargos e os conduziram com muito sucesso.

Obrigado pela presença de todos.

Esperamos que a ERAD/RS 2021 seja muito proveitosa.

Um abraço,

Maurício Pillon (UDESC), Márcio Castro (UFSC) e Claudio Schepke (UNIPAMPA)

Coordenadores gerais da ERAD/RS 2021

#### Mensagem da Coordenação dos Minicursos

A Escola Regional de Alto Desempenho da Região Sul (ERAD/RS) é um evento anual promovido pela Sociedade Brasileira de Computação (SBC) e pela Comissão Regional de Alto Desempenho da Região Sul (CRAD/RS). A escola, que neste ano completa os seus vinte e um anos, foi realizada entre os dias 14 e 16 de abril de 2021, na cidade de Joinville/SC, no campus sede da Universidade do Estado de Santa Catarina (UDESC). Essa foi a primeira vez que a escola foi realizada fora do estado do Rio Grande do Sul.

Um dos objetivos da ERAD/RS é qualificar profissionais da região sul nas diversas áreas do Processamento de Alto Desempenho (PAD). Com este intuito, todo o ano, são selecionados minicursos introdutórios, intermediários e avançados em tópicos de interessa à comunidade. Não diferente, neste ano, foram selecionados seis minicursos, dos quais todos viraram capítulos para este livro. Os minicursos aqui representados, apresentam tópicos de ponta da área de PAD, os quais irão certamente contribuir e agradar os participantes do evento.

Os coordenadores dos minicursos agradecem aos autores, por compartilharem seus conhecimentos através da submissão de minicursos de alto nível para esta edição da escola, aos coordenadores e organizadores da ERAD/RS, pelo apoio dado na seleção dos minicursos e na realização do evento, além de desejar uma boa ERAD/RS a todos!

Andrea Charão (UFSM) e Matheus S. Serpa (UFRGS) Coordenadores dos Minicursos da ERAD/RS 2021

### **Comitês Organizadores**

#### Coordenação Geral

- Maurício Aronne Pillon (UDESC Joinville)

- Márcio Castro (UFSC Florianópolis)

- Claudio Schepke (UNIPAMPA Alegrete)

#### Coordenação Local

- Charles Christian Miers (UDESC Joinville)

- Ricardo Pfitscher (UFRGS/UNISOCIESC)

#### Fórum de Pós-Graduação

- Guilherme Piêgas Koslovski (UDESC Joinville)

- Tiago Ferreto (PUCRS)

#### Fórum de Iniciação Científica

- Odorico Mendizabal (UFSC)

- Marco A. Zanatta Alves (UFPR)

#### **Minicursos**

- Andrea Charão (UFSM)

- Matheus Serpa (UFRGS)

## Minicursos

| Minicurso 1                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------|

| Desvendando o Uso de Contadores de Hardware para Otimizar Aplicações de Inteligência Artificial                                     |

| Valéria Girelli (UFRGS), Félix Dal Pont Michels (UFRGS), Francis Birck Moreira (UFPR),<br>Philippe Olivier Alexandre Navaux (UFRGS) |

| Minicurso 2                                                                                                                         |

| Otimização de Programas Paralelos com uso do OpenACC                                                                                |

| Minicurso 3                                                                                                                         |

| Are you root? Experimentos Reprodutíveis em Espaço de Usuário                                                                       |

| Minicurso 4                                                                                                                         |

| Além de Simplesmente: #pragma omp parallel for                                                                                      |

| Minicurso 5                                                                                                                         |

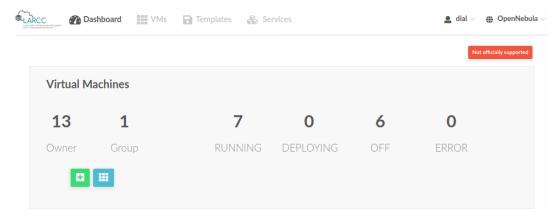

| Ambiente de Nuvem Computacional Privada para Teste e Desenvolvimento de Programas Paralelos                                         |

| Minicurso 6                                                                                                                         |

| Desenvolvimento de Aplicações Baseadas em Tarefas com OpenMP Tasks                                                                  |

## Capítulo

1

# Desvendando o Uso de Contadores de *Hardware* para Otimizar Aplicações de Inteligência Artificial

#### Valéria S. Girelli

vsgirelli@inf.ufrgs.br Grupo de Processamento Paralelo e Distribuído (GPPD) Universidade Federal do Rio Grande do Sul (UFRGS) Sala 209, Prédio 67, Instituto de Informática - Campus do Vale 91501-970 - Porto Alegre - RS - Brasil

#### Félix D. P. Michels

felix.junior@inf.ufrgs.br Grupo de Processamento Paralelo e Distribuído (GPPD) Universidade Federal do Rio Grande do Sul (UFRGS) Sala 201, Prédio 67, Instituto de Informática - Campus do Vale 91501-970 - Porto Alegre - RS - Brasil

#### Francis B. Moreira

fbm@inf.ufpr.br High Performance Systems (HiPES) Universidade Federal do Paraná (UFPR) Sala 84, Departamento de Ciência da Computação - Centro Politécnico 81531-980 - Curitiba - PR - Brasil

#### Philippe O. A. Navaux

navaux@inf.ufrgs.br Grupo de Processamento Paralelo e Distribuído (GPPD) Universidade Federal do Rio Grande do Sul (UFRGS) Sala 210, Prédio 67, Instituto de Informática - Campus do Vale 91501-970 - Porto Alegre - RS - Brasil

#### Resumo

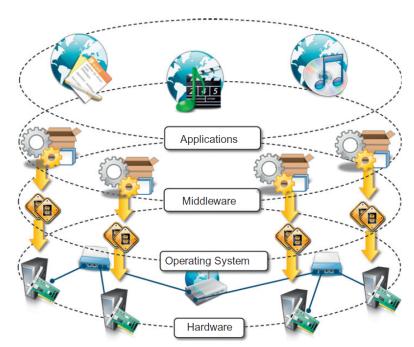

O desempenho dos sistemas computacionais aumentou consideravelmente nas últimas décadas. Tal avanço se deu por meio de mecanismos que nem sempre são visíveis para o usuário final, como o sistema de memória e o sistema de prefetching, que possuem grande impacto no desempenho de processadores modernos. Ao mesmo tempo, algoritmos de Inteligência Artificial (IA) se tornam cada vez mais relevantes em diversas áreas da computação e da sociedade, e requerem um crescente poder computacional. Com isso, para se obter o máximo desempenho dessas aplicações, é necessário garantir que as mesmas estejam utilizando da melhor forma esses recursos. Para auxiliar na avaliação da utilização desses mecanismos transparentes ao usuário, muitos processadores e aceleradores modernos fornecem contadores de hardware, estruturas que permitem o monitoramento de eventos internos, como o número de acessos à memória e a porção de dados encontrados em cada nível de memória. Portanto, neste capítulo abordaremos a utilização de contadores das arquiteturas Intel Xeon Cascade Lake e NEC SX-Aurora TSUBASA para analisar o desempenho das cada vez mais frequentes aplicações de IA. Por meio das ferramentas Linux perf e NEC FTRACE é possível acessar esses contadores e utilizar os resultados para identificar gargalos nessas aplicações.

#### 1.1. Introdução

Aplicações de Inteligência Artificial (IA) vêm ganhando cada vez mais relevância nos mais diversos espaços da sociedade (A et al., 2019). De jogos como Xadrez e Poker, ao tratamento de doenças como câncer, análise de mudanças climáticas, reconhecimento visual, de fala e detecção de fraudes em transações bancárias, são quase incontáveis os campos do nosso dia a dia nos quais a IA tem se introduzido. Diversos trabalhos também propõem a aplicação de IA para aprimorar o desempenho de sistemas computacionais, como mecanismos de *prefetching* (Liao et al., 2009; Peled et al., 2015; BHATIA et al., 2019) e de predição de desvio (Zangeneh et al., 2020; Zhang et al., 2020), que fazem uso de heurísticas na tomada de decisão.

A crescente relevância da área é acompanhada pelo aumento na quantidade de dados sobre os quais as aplicações de IA trabalham. A quantidade de dados e informações digitais no mundo hoje ultrapassa os 44 trilhões de gigabytes. Dessa forma, surge a necessidade de um poder computacional cada vez maior, e muitas empresas migram seus serviços para grandes servidores de processamento de dados com milhares de núcleos e centenas de GPUs em busca de tempos de execução menores. Com a utilização desses sistemas computacionais, surge também a preocupação com o consumo energético e com a refrigeração. É necessário, portanto, garantir que aplicações de Inteligência Artificial estejam utilizando eficientemente os recursos computacionais a sua disposição, e desenvolvedores e desenvolvedoras das diversas bibliotecas voltadas à IA empregam grandes esforços na otimização de suas ferramentas.

Além de aplicações de IA, diversas aplicações de *High-Performance Computing* (HPC) fazem uso desses sistemas equipados com centenas de núcleos e GPUs. A importância de se alcançar o mais alto desempenho possível nessas aplicações levou a uma grande variedade de ferramentas de análise de desempenho. Tais ferramentas permitem a identificação de comportamentos que levam à redução de desempenho e auxiliam no

desenvolvimento de otimizações nas aplicações. Exemplos dessas ferramentas são o *framework* HPCToolkit (ADHIANTO et al., 2009), Periscope (GERNDT; FÜRLINGER; KEREKU, 2005), o projeto TAU (SHENDE; MALONY, 2006), Vampir (KNÜPFER et al., 2008) e Score-P (MEY et al., 2012). No entanto, as informações providas por esses mecanismos são geralmente de mais alto nível e menos detalhadas. Com isso, a identificação de gargalos provenientes da utilização ineficiente dos componentes disponíveis na arquitetura se torna mais desafiadora. Além disso, por serem ferramentas complexas e que coletam informações em diferentes níveis do sistema ao mesmo tempo, o *overhead* e ruído sobre a execução das aplicações tendem a ser altos.

Uma alternativa a essas ferramentas é a utilização de contadores de *hardware*, estruturas encontradas em muitos processadores e aceleradores modernos que permitem o monitoramento de eventos internos a essas arquiteturas. Alguns desses eventos são o número de instruções executadas, o número de ciclos, o número de acessos à memória, dentre outros. Por meio da utilização desses contadores é possível realizar a coleta de informações de forma mais específica e detalhada se comparado às informações obtidas com outras ferramentas de mais alto nível. O usuário tem a possibilidade de identificar as informações que estão disponíveis para sua arquitetura específica e combinar diferentes contadores afim de investigar aspectos distintos. Além disso, contadores de diferentes núcleos também podem ser combinados, analisando-se o sistema como um todo. Dessa forma, utilizar contadores de *hardware* para analisar o desempenho de aplicações parale-las permite que o usuário tenha mais controle sobre o processo, com menos ruído sobre a aplicação.

Portanto, ao longo deste capítulo iremos estudar aspectos de duas arquiteturas distintas, alguns de seus contadores de *hardware* e como utilizar ferramentas de *profiling* para acessar essas informações. Com base nisso, será possível analisar o desempenho de aplicações de Inteligência Artificial e propor otimizações em seus códigos.

O capítulo está organizado da seguinte maneira: na Seção 1.2 é feita uma introdução à arquitetura de computadores, demonstrando conceitos como *pipeline*, arquiteturas superescalares, entre outros. Em seguida, na Seção 1.3 temos uma discussão sobre hierarquia de memória e sistema de *prefetching*. A Seção 1.4 é apresentada uma breve explicação sobre vetorização, exemplificando com a arquitetura vetorial NEC SX-Aurora TSUBASA. A Seção 1.5 expõe os ambientes de execução utilizados na elaboração desse minicurso. A Seção 1.6 apresenta os contadores de *hardware* e a utilização das ferramentas Linux perf e o NEC FTRACE. Na Seção 1.7, conceitos de Inteligência Artificial e Aprendizado de Máquina são apresentados, bem como a aplicação utilizada neste minicurso. Por fim, na Seção 1.8 utilizamos exemplos práticos aplicados em uma implementação de retro-propagação, otimizando-a por meio da utilização de contadores de *hardware*, seguindo para a conclusão deste curso, na Seção 1.9.

#### 1.2. Arquitetura de Computadores

A rápida evolução na área de arquitetura de computadores é baseada em três fatores relacionados: tamanho dos componentes, paralelismo entre componentes, e especulação (HENNESSY; PATTERSON, 2017). O tamanho dos componentes, ou tamanho do processo de fabricação, define a largura em nanômetros dos transistores do sistema. Quanto menor

Figura 1.1. Multiplicador de 32 bits com carry pré-calculado. Fonte: Bokade et al. (BOKADE; DAKHOLE, 2016), pág. 5.

o transistor, mais *hardware* conseguimos colocar dentro do *chip* do processador ou memória, menor a latência de fio dos componentes e entre os mesmos, e portanto maior a frequência de operação (FLOYD, 2010). Já o paralelismo implica em usar mais *hardware* para produzir mais trabalho no mesmo período de tempo, sendo usado em todos os níveis de arquitetura. Um exemplo claro é a diferença existente entre um somador por propagação e um somador com *carry* pré-calculado. O somador normal precisa de um tempo igual à soma dos tempos de todos somadores já que cada somador depende do resultado do somador predecessor. Já o somador com *carry* pré-calculado utiliza *hardware* adicional para calcular *carries* em paralelo, permitindo que todos os somadores terminem seu serviço em paralelo. Este paralelismo pode ser considerado o paralelismo a nível de "operação", onde torna-se uma operação mais eficiente ao adicionar *hardware* para tal fim (FLOYD, 2010).

#### 1.2.1. Pipeline

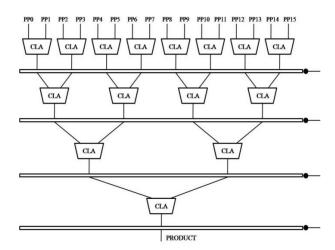

Uma técnica muito utilizada para paralelismo é a técnica de *pipeline* (HENNESSY; PATTERSON, 2017). Como operações de multiplicação e divisão são muito demoradas, é comum dividir elas em vários estágios com o uso de registradores intermediários, como na Figura 1.1. Assim é possível reduzir o caminho crítico do sistema e manter uma frequência de operação mais alta. Com isso, tem-se capacidade de realizar mais operações em menos tempo, pois conforme uma instrução termina um estágio, este está pronto para começar uma nova instrução. A ideia de *pipeline* foi adotada em larga escala para todo o funcionamento do processador. Processadores antigos utilizam de frequência mais baixa e um conjunto grande de instruções complexas, recebendo a caracterização de CISC (*Complex Instruction Set Computer*) (ISEN; JOHN; JOHN, 2009). Em 1981, Hennessy desenvolveu o processador MIPS (*Microprocessor without Interlocked Pipeline Stages*) (HENNESSY et al., 1982), que implementa um conjunto pequeno de instruções simples, permitindo uma grande inovação: o uso de *pipeline* para a operação de todas as instruções. Hoje este tipo de computador é conhecido como RISC (*Reduced Instruction Set Computer*) (ISEN; JOHN; JOHN, 2009).

Figura 1.2. pipeline da arquitetura MIPS. Fonte: Hennessy & Patterson (PATTERSON; HENNESSY, 2004), pág. 387

A ideia, demonstrada na Figura 1.2, é separar as instruções em 5 estágios: busca (IF), decodificação (DEC), execução (EXE), acesso à memória (MEM), e escrita (WB). Assim, quando uma instrução termina de executar um estágio e passa para o próximo, o processador já pode receber uma nova instrução. Isto permite um paralelismo a nível de operação do processador, pois temos múltiplas instruções no processador, utilizando seus diferentes estágios, embora realisticamente ainda entregaremos no máximo uma instrução por ciclo. O pipeline também permite um grande aumento na frequência ao reduzir o caminho crítico para o tempo de um estágio, e faz melhor uso dos recursos do processador, pois boa parte dos recursos ficava inativa enquanto as instruções não estivessem usando elas. Um dos problemas do pipeline é que existem dependências entre certas operações como saltos e leitura após escrita, onde é necessário inserir bolhas no pipeline para operações terem os valores corretos. Assim o número de instruções entregues por ciclo geralmente é menor que um, o que é resolvido através de técnicas de especulação, como predição de salto (YEH; PATT, 1991).

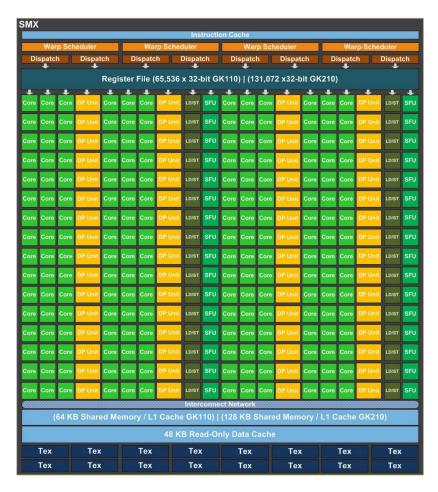

#### 1.2.2. Arquiteturas Superescalares

Neste mesmo princípio, nota-se que várias unidades funcionais ficam inativas quando outra operação está sendo executada. Assim, desenvolveu-se a arquitetura superescalar (THORNTON, 1980), com o propósito de aumentar o paralelismo a nível de instrução (*instruction level parallelism* – ILP). A arquitetura de *pipeline* superescalar é basicamente uma arquitetura *pipeline* de maior capacidade: o processador é capaz de buscar múltiplas instruções em um ciclo, decodificar múltiplas instruções em um ciclo, mandar múltiplas instruções para execução nas diferentes unidades funcionais, mandar múltiplas requisições para a memória, e fazer múltiplas escritas nos registradores. Uma arquitetura

superescalar não é necessariamente uma arquitetura *pipeline*, pois as técnicas são distintas (HENNESSY; PATTERSON, 2017). Para o correto funcionamento, são necessárias várias adições ao processador, como *buffers* entre os estágios, a adição de estágios como a renomeação de registradores (o qual elimina dependências falsas entre as instruções) e o estágio de despacho (o qual possui lógica inteligente adicional para despachar instruções na melhor ordem conforme o estado do processador), um *buffer* de reordenação de instruções (*reorder buffer* - ROB), *buffers* de ordem para requisições à memória (*memory order buffer* - MOB), entre outros (FOG, 2012).

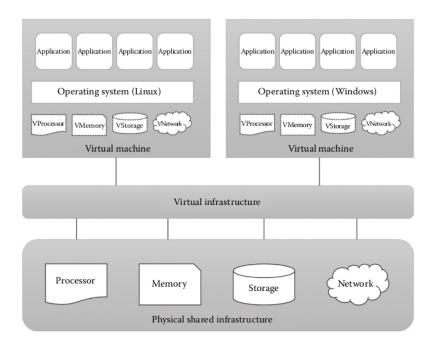

#### 1.2.3. Threading

A adição de tantas estruturas para melhorar o desempenho de um *pipeline* superescalar inseriu problemas nas arquiteturas modernas. Problemas como a espera por resolução de saltos e por acessos à memória limitam o número de instruções alcançadas em testes reais. O número de instruções por ciclo (*instructions per cycle* – IPC) na maior parte dos programas não passa de 2, apesar de processadores dimensionados para mais de 4 instruções em paralelo. Para dados contíguos, adotou-se vetorização, que é o paralelismo no nível de operação da instrução, a qual agora recebe mais dados para uma operação. Para programas mais complexos, criou-se um novo nível de paralelismo: o paralelismo de *threads* (*Thread Level Parallelism* – TLP). Agora, o processador é capaz de escalonar mais de um fluxo de programa ao manter múltiplos contadores de programa (*Program Counter* - PC) e conjuntos de registradores lógicos para representar o estado de diferentes *threads* (fios). Este suporte ocorre em dois níveis: arquiteturas *multithreaded* e arquiteturas multi-core.

Em arquiteturas *multithreaded*, o núcleo de processamento possui a capacidade de dividir os seus recursos entre múltiplas *threads* (TULLSEN; EGGERS; LEVY, 1995). O *buffer* de reordenamento, as estações de espera por execução em cada unidade funcional, o banco de registradores, e todas as outras estruturas de controle são divididas entre as múltiplas *threads* para que todas ocupem de forma eficiente as unidades funcionais do core. Entre as formas de *multithreading* podemos citar:

- *Multithreading* entrelaçado, no qual o núcleo busca uma instrução de cada *thread* a cada ciclo;

- *Multithreading* em bloco, onde a cada período de ciclos o processador busca várias instruções da mesma *thread*, e troca a *thread* quando acaba o período;

- *Multithreading* simultâneo, hoje adotado pela Intel como *Hyperthreading* (MARR et al., 2002), onde instruções de todas as *threads* são buscadas no mesmo ciclo.

Em arquiteturas multi-core, possuímos múltiplos *cores*, os quais podem ter apenas uma *thread*, ou podem ser *multithreaded* (BLAKE; DRESLINSKI; MUDGE, 2009). O sistema operacional encarrega-se de gerenciar os recursos dos múltiplos *cores*, permitindo o processamento paralelo e o mapeamento da execução conforme desejado nos *cores* disponíveis.

#### 1.2.4. Especulação

Através da evolução da arquitetura, vários problemas foram identificados na busca de execução eficiente. Mecanismos de especulação tentam contornar estes problemas ao prever o comportamento da aplicação em relação a eles. Por exemplo, a latência da memória se tornou cada vez maior devido à evolução muito mais rápida do processador, tornando o acesso a instruções e dados um gargalo. Para diminuir a latência da memória, a memória cache foi adotada, a qual serve como armazenamento temporário para linhas de memória, com tamanho e latência muito menores (JACOB; WANG; NG, 2010). A primeira premissa da memória cache é de que um dado recentemente usado será reusado em breve, o que é uma especulação ou predição em relação ao comportamento da aplicação, onde assume-se localidade temporal. A segunda premissa comum em memória cache ao usar linhas longas com múltiplos endereços é de que dados contíguos serão usados em um curto espaço de tempo, portanto assume-se localidade espacial, o que é praticamente sempre válido para acessos à instruções na memória, por exemplo. Entre outros mecanismos de especulação, podemos citar a desambiguação de leituras, a predição de saltos, prefetching, buffers de linha na memória principal (Dynamic Random-Access Memory – DRAM) (JACOB; WANG; NG, 2010), entre outros.

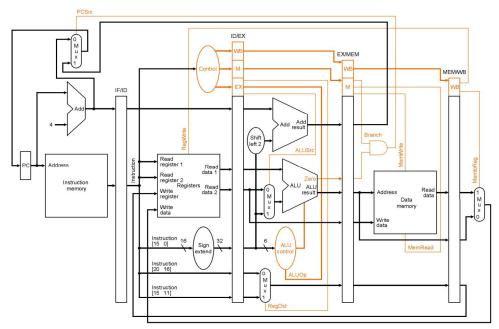

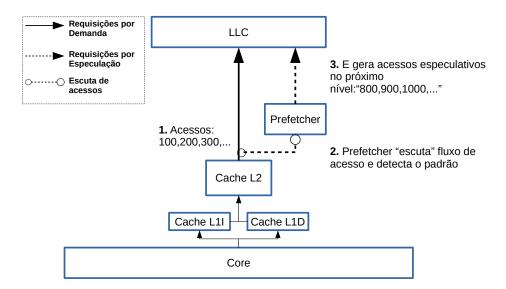

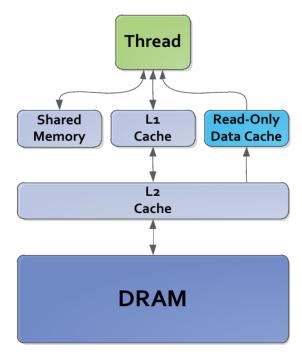

#### 1.3. Hierarquia de Memória e Sistema de Prefetching

Em processadores modernos, uma hierarquia de *cache* em três níveis é comumente usada (MORGAN, 2017; CUTRESS, 2017). Nessa configuração, o primeiro nível de *cache* de dados (L1) e o segundo nível de *cache* de dados (L2) são normalmente privados a cada núcleo do processador. Esses níveis de *cache* são mais próximos fisicamente do processador, possuem menor capacidade de armazenamento, e permitem acesso aos dados de forma mais eficiente. Um terceiro nível de *cache* (L3, também conhecida por *Last Level cache* – LLC) é compartilhada entre todos os núcleos do processador. Seu tempo de resposta é frequentemente maior que o tempo de resposta dos níveis de *cache* privados, mas com a vantagem de permitir uma capacidade de armazenamento maior. Uma representação dessa hierarquia é observada na Figura 1.3.

Quando o processador emite uma requisição por um dado na memória, diversas situações podem ocorrer. Inicialmente, a requisição é entregue à *cache* L1, que é relativamente pequena (32 KiB) e possui uma baixa latência de acesso (4 ciclos de processador) (FOG, 2012; HENNESSY; PATTERSON, 2017). Caso o dado seja encontrado nesse nível de *cache* ele é rapidamente entregue ao processador. No entanto, devido à capacidade limitada da *cache* L1, por muitas vezes os dados não estão presentes, e a busca pelo dado é repetida no próximo nível de *cache*. Cada vez que um dado não é encontrado em um nível de *cache* tem-se um *cache miss* e a necessidade de repetir o procedimento de busca em um nível mais distante do processador, cujo tempo de acesso é maior (e somado aos tempos de acesso dos níveis de memória predecessores). Portanto, encontrar os dados solicitados em níveis de *cache* mais próximos do processador é preferível, caso contrário, a hierarquia da memória pode se tornar um grande gargalo para o desempenho das aplicações (BAKHSHALIPOUR et al., 2019).

Cabe ressaltar, no entanto, que diversas outras ações são necessárias juntamente com o processo de busca por dados descritos acima, como por exemplo o acesso à *Trans*-

Figura 1.3. Exemplo da hierarquia de memória de um processador moderno. Conforme nos afastamos do processador, as memórias se tornam maiores e mais lentas.

lation Lookaside Buffer (TLB) (onde é possível verificar se a página de dados está fisicamente presente na memória principal e a tradução do endereço virtual para o físico (HENNESSY; PATTERSON, 2017)), possíveis acessos à memória principal para consulta da tabela de páginas (um procedimento custoso devido à alta latência da memória DRAM), e ainda transferências de dados entre duas *caches* de diferentes núcleos do sistema devido à ação do protocolo de coerência de *cache*.

Nos últimos anos, várias melhorias no desempenho do processador têm sido observadas, como o aumento do número de núcleos – o que requer memórias com maior largura de banda de transferência de dados para lidar com as requisições de dados emitidas por esses diversos núcleos, e a capacidade do processador de requisitar vários dados por ciclo (multiple issue) (HENNESSY; PATTERSON, 2017). No entanto, as tecnologias de memória não melhoraram tanto quanto os processadores, criando uma lacuna de desempenho referida na literatura como Memory Wall (WULF; MCKEE, 1996). Vários problemas podem surgir dessa disparidade de desempenho. Por exemplo, se uma instrução for um *load* (requisição de dado para leitura) e seus dados necessários não forem entregues rapidamente pelo sistema de memória, a execução dessa instrução e das instruções dependentes a ela podem ser interrompidas (HENNESSY; PATTERSON, 2017). Para evitar tais paralisações, deve-se reduzir o número de ciclos desde o momento em que o processador emite uma requisição até o momento em que pode realmente usar os dados deve ser o menor possível. Além disso, dada a natureza de multiple issue dos processadores modernos, um grande número de solicitações de memória pode ser emitido em apenas alguns ciclos, possivelmente criando contenção em algum nível da hierarquia de memória.

Diante desses vários problemas, o *prefetcher* foi criado para mitigar a latência da memória (BAER; CHEN, 1991). *Prefetching* é uma técnica implementada em *hardware* que visa prever quais serão os próximos endereços de memória a serem solicitados pelo processador. Ao monitorar as solicitações de memória anteriores, o *prefetcher* é capaz

Figura 1.4. Abstração do comportamento de um prefetcher.

de identificar possíveis padrões de acesso. Com base nesses padrões, ele especula quais podem ser os próximos endereços a serem solicitados e, em seguida, realiza requisições com antecedência, antes que o processador realmente precise dos dados. Assim, quando o dado for finalmente solicitado pelo processador, ele já estará em níveis de *cache* mais próximos (HENNESSY; PATTERSON, 2017). A latência da memória principal acima mencionada é, portanto, ocultada por outras instruções anteriores à instrução que de fato realizou a requisição dos dados buscados pelo *prefetcher*.

Com os dados já em níveis mais próximos, (i) a crítica *load-to-use latency* pode ser reduzida (KANG; WONG, 2013; Guttman et al., 2015), e (ii) uma importante métrica de desempenho é melhorada, a taxa de acertos da *cache*, também conhecida como *cache hit*. A taxa de *hits* representa a porção de requisições que são encontradas em um determinado nível de *cache* sem a necessidade de se aprofundar na hierarquia de memória – que, consequentemente, resultaria em um tempo de execução maior. Esses ganhos de desempenho permitiram que os *prefetchers* se tornassem um mecanismo predominante nas arquiteturas atuais (MORGAN, 2017; CUTRESS, 2017; FOG, 2012; GIRELLI et al., ). Exemplos de padrões identificados por mecanismos de *prefetcher* comuns são *stride* (CHEN; BAER, 1995) e *stream* (LE et al., 2007).

A Figura 1.4 mostra um exemplo de *prefetcher* da *cache* L2 detectando um padrão de acesso *stride*. A *cache* L2 encaminha requisições para a LLC (mostrado na Figura 1.4 como o evento 1). O *prefetcher* da L2, por sua vez, intercepta essas solicitações "escutando" a interconexão da *cache* (evento 2) e identificando o padrão de acesso que está sendo gerado. Com base no padrão identificado, requisições especulativas são inseridas no *Miss Status Holding Register* (MSHR) da *cache* L2 (3), um *buffer* que mantém o controle de eventos de *miss* que ainda precisam ser tratados. Essas requisições especulativas inseridas no MSHR da L2 são feitas primeiramente à *cache* L2 para evitar a busca redundante de um dado que já reside na L2. Esses acessos são vistos como solicitações regulares feitas à L2 pelo *prefetcher*, de modo que a L2 não precisa realmente encaminhar a resposta para a

L1. Se o endereço especulado ainda não estiver presente na L2, a L2 encaminha a requisição por dado para os próximos níveis da hierarquia, como em um acesso normal. Assim, quando o processador precisar de um dado solicitado previamente pelo *prefetcher*, ele já estará em um nível de *cache* mais próximo (neste caso, a *cache* L2).

#### 1.4. Vetorização

A característica chave das arquiteturas vetoriais é seu modelo *Single Instruction Multiple Data* (SIMD). Em processadores superescalares, o dado padrão é uma palavra de normalmente 32 *bits* sobre a qual um conjunto de instruções atua de maneira individual. Já em uma arquitetura vetorial, uma instrução vetorial é aplicada simultaneamente sobre uma coleção de palavras em formato de vetor (HENNESSY; PATTERSON, 2017). Desse modo, tem-se a execução de uma mesma instrução (*single instruction*) sobre múltiplos dados (*multiple data*) em um único ciclo. Por conta disso, processadores vetoriais têm a vantagem de que cada dado é independente entre si, o que permite que a mesma instrução seja realizada sobre todos eles ao mesmo tempo.

Por operar em um número maior de dados de uma única vez, instruções vetoriais resultam em menos buscas por dados e menos *branches* quando os dados estão contíguos. Com isso é possível reduzir-se o número de erros de predição e a latência de acesso à memória, favorecendo o tempo de execução de uma aplicação(KSHEMKALYANI, 2012). Porém, essa vantagem é relevante apenas quando há blocos de memória suficientemente grandes, onde haveria uma grande latência de acesso a memória em um processador escalar tradicional.

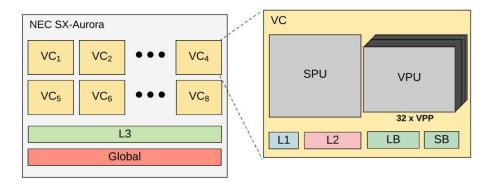

Um exemplo de arquitetura vetorial é a SX-Aurora TSUBASA da empresa NEC Corporation. Esse processador possui 8 núcleos de processamento executando com frequência de 1,408 GHz e 3 níveis de memória *cache* (KOMATSU et al., 2018). Uma das vantagens dessa arquitetura em relação as outras existentes é o tamanho das unidades vetoriais da mesma, podendo chegar a 256 elementos de 64 bits. Além disso, o compilador da NEC (NEC, 2020a) toma decisões automaticamente , identificando áreas nas quais é possível gerar código vetorizável sem que haja a necessidade de alteração do código fonte. Entretanto, o compilador ainda necessita de ajuda do programador para facilitar a interpretação do código. O programador pode utilizar diretrizes específicas e utilizar técnicas de otimização como *loop unrolling* e *inlining*.

#### 1.5. Ambiente de Execução

O ambiente de execução utilizado nos experimentos estão presentes na infraestrutura PCAD¹, no INF/UFRGS. Na Tabela 1.1 tem-se as características do *Vector Engine* (VE) TSUBASA. A máquina vetorial consiste em um ambiente com 8 cores, 48GB de memória global a 900 MHz e *cache* L3 compartilhada de 2 MB. Cada core possui memórias *caches* privadas, L1 de instrução e dados de 32KB cada e L2 de 256KB, uma unidade de processamento escalar (*Scalar Processing Unit* – SPU) e uma unidade de processamento vetorial (*Vector Processing Unit* – VPU), sendo que cada VPU contém *load buffer*, *store buffer*, e 32 *pipelines* paralelos vetoriais (*Vector Parallel Pipeline* – VPP) (NEC, 2020b). A maior parcela dos cálculos é feita pela VPU, sendo a SPU responsável pelos traba-

<sup>&</sup>lt;sup>1</sup><http://gppd-hpc.inf.ufrgs.br>

Figura 1.5. Ambiente de execução SX-Aurora.

Tabela 1.1. Arquitetura SX-Aurora (Vector Engine Type 10BE).

| Processador      | 8 cores @ 1408 MHz            |

|------------------|-------------------------------|

| Microarquitetura | SX-Aurora                     |

| Cache            | 8 X 32 KB L1I; 8 X 32 KB L1D; |

|                  | 8 X 256 KB L2; 8 X 2 MB L3    |

| Memória          | HBM2 48 GB, 900 MHz           |

lhos sequenciais, bem como as tarefas do sistema operacional. Na figura 1.5 temos uma representação gráfica desses componentes.

Já o *Vector Host* (VH) é representado pela microarquitetura Intel Cascade Lake. Na Tabela 1.2 tem-se as especificações do processador Intel Xeon Gold 6226, que possui 12 núcleos operando a uma frequência entre 2.7 GHz e 3.7 GHz. Cada núcleo possui 32 KB de *cache* L1 de dados e instruções, bem como uma cache L2 também privada de 1 MB. A L3, compartilhada entre todos os núcleos, possui capacidade de 16,5 MB, e a máquina ainda apresenta 192 GB de memória DRAM. A microarquitetura Cascade Lake é bastante semelhante à sua predecessora Skylake, porém a Cascade Lake introduz suporte à instruções de Rede Neural Vetorial AVX-512 (*AVX-512 Vector Neural Network Instructions* – VNNI) (PEREZ et al., 2018).

#### 1.6. Contadores de Hardware

Após compreendermos melhor o funcionamento de arquiteturas superescalares e vetoriais e alguns de seus pontos de perda de desempenho, agora é necessário compreender-

Tabela 1.2. Microarquitetura Cascade Lake (Xeon Gold 6226).

| Processador      | 12 cores @ 2700 - 3700 MHz;     |

|------------------|---------------------------------|

| Microarquitetura | Cascade Lake                    |

| Cache            | 12 X 32 KB L1I; 12 X 32 KB L1D; |

|                  | 12 X 1 MB L2; 16,5 MB L3        |

| Memória          | DDR4 192 GB, 2933 MHz           |

mos como obter informações a respeito do *hardware* no momento da execução de uma aplicação afim de melhorarmos o desempenho de uma aplicação. Arquiteturas modernas permitem a utilização de contadores de *hardware*, estruturas internas que permitem o monitoramento de eventos da execução e funcionamento do processador ou acelerador. Como já citado anteriormente, diversas ferramentas de *profiling* foram desenvolvidas que permitem acesso a contadores de *hardware*. Neste capítulo, nós apresentamos os contadores existentes na arquitetura Intel Cascade Lake e no processador vetorial SX-Aurora TSUBASA e como acessá-los por meio das ferramentas Linux perf e NEC FTRACE, respectivamente.

#### 1.6.1. Linux perf

Linux perf é uma ferramenta de *profiling* para sistemas Linux que permite acesso à interface perf\_events de eventos de desempenho presentes em arquiteturas superescalares. A utilização da ferramenta é feita por linha de comando por meio do comando perf, e é possível listar os eventos disponíveis na plataforma por meio do comando perf list. Um comando comumente utilizado para análise de desempenho é o comando stat, que permite a coleta de informações referentes à execução de uma aplicação. Com a utilização da opção –e é possível listar os eventos que se deseja coletar. O exemplo abaixo representa a linha de comando necessária para a coletar informações a respeito do número de instruções e do número de ciclos de CPU necessários para a execução do comando ls:

```

1 perf start -e instructions, cpu-cycles ls

```

Além de realizar a execução do comando ls e listar o conteúdo do diretório atual, a execução do comando perf stat com os eventos instructions e cpu-cycles dá um resultado semelhante ao observado abaixo:

```

1 Performance counter stats for 'ls':

2     1.309.712 instructions # 0,71 insnt per cycle

3     1.848.886 cycles

4     0,000800891 seconds time elapsed

```

É importante notar que as arquiteturas superescalares normalmente possuem um número limitado de contadores de *hardware*. Uma vez que cada contador de *hardware* pode ser utilizado para monitoramento de um único evento a cada dado momento, a quantidade de eventos que podem ser monitorados simultaneamente é limitada. Para possibilitar o monitoramento de um número maior de eventos, a ferramenta perf realiza uma técnica de multiplexação do tempo de monitoramento, permitindo que cada evento possua uma parcela do tempo de utilização do contador. No entanto, o que esta abordagem possibilita é apenas uma estimativa do real comportamento da aplicação, uma vez que os eventos multiplexados não são monitorados o tempo todo com exclusividade. Dessa forma, é aconselhável que cada evento seja monitorado individualmente por meio da instrução perf stat, realizando o *profiling* da aplicação várias vezes.

#### 1.6.2. NEC FTRACE

Desenvolvida pela empresa NEC, a ferramenta FTRACE pode ser utilizada para a obtenção de informações de contadores de *hardware* presentes na arquitetura vetorial da NEC. Para utilizar a ferramenta é necessário recompilar a aplicação utilizando o compilador de-

senvolvido pela empresa NEC. Para aplicações escritas em linguagem C usamos o ncc, para aplicações C++ usamos o nc++ e para aplicações Fortran usamos o nfort. Além disso, é necessário adicionar a *flag* de compilação -ftrace, como exibido no exemplo: ncc -ftrace source.c. A partir disso, podemos executar a aplicação como faríamos com um executável comum. Ao fim da execução, o arquivo de informações ftrace.out é gerado, podendo ser lido por meio da mesma ferramenta (e direcionando a saída para o arquivo *output*):

```

1 ftrace -f ftrace.out >> output

```

O arquivo gerado possui diversas informações. A Figura 1.7 mostra todas as informações de saída que a ferramenta FTRACE proporciona. Dentre elas podemos destacar o tempo total de execução, o nome das funções executadas, o número de vezes que cada função foi chamada, porcentagem de utilização de core por cada função, informações a respeito do número de *misses* dos diversos níveis de *cache*, dentre outros. É possível ainda controlar o tipo de informações que se deseja por meio dos dois diferentes modos de *profiling* indicados por meio da variável de ambiente VE\_PERF\_MODE. Caso a variável possua valor VECTOR-OP ou esteja indefinida (assumindo o valor padrão), o FTRACE gera informações relacionadas principalmente às instruções vetoriais. Caso o valor da variável VE\_PERF\_MODE seja VECTOR-MEM, os dados levantados correspondem principalmente a acessos à memória. Dessa forma, pode ser proveitoso fazer uso dos dois modos e agregar seus resultados ao fim. Pode-se alterar o valor da variável de ambiente VE\_PERF\_MODE, para um dos dois modos, da seguinte forma:

```

1 export VE_PERF_MODE=VECTOR-OP

2 export VE_PERF_MODE=VECTOR-MEM

```

#### 1.7. Aplicações de Inteligência Artificial

Com a evolução de arquiteturas de processadores e os sistemas agregados, e.g. memória e aceleradores, algoritmos cada vez mais complexos, com grande volume de dados e operações, acharam aplicações práticas em computadores. Uma subárea da computação tornou-se o expoente atual na demanda por sistemas mais poderosos: desenvolvida na estatística, o Aprendizado de Máquina, mais genericamente conhecido como Inteligência Artificial, é a área em voga nos dias de hoje (GADEPALLY et al., 2019).

A base estatística para aprendizado de máquina é a inferência estatística, um ramo da estatística a qual tem por base o estudo de modelos preditivos baseados em amostras de uma população, tendo como principais escolas a Inferência Frequentista e a Inferência Bayesiana (CASELLA; BERGER, 2021). Quanto melhor a qualidade dessa amostra, melhor a capacidade de predição do modelo, o que muitos pesquisadores interpretam também como uma amostra de tamanho maior. Portanto, estes modelos processam um grande volume de dados para ajustar seus parâmetros de modo a melhorar suas predições.

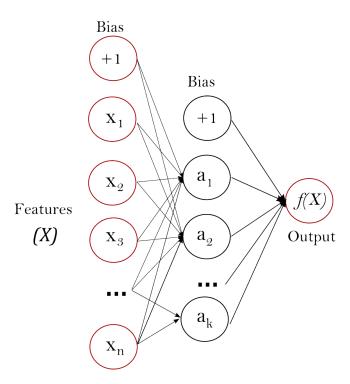

Boa parte destes modelos assume que existe uma função de "erro", a qual depende dos parâmetros do modelo. O algoritmo para treinar um modelo, portanto, consiste em testar várias amostras contra o modelo atual, e ajustar os parâmetros conforme o erro do modelo em prever o comportamento das amostras. Ao chegar em um mínimo local desta função de erro, avalia-se a qualidade do modelo, potencialmente aplicando-se uma reran-

Figura 1.6. Rede Neural do tipo perceptron de múltiplas camadas.

domização de parâmetros para procurar um mínimo local melhor, embora não existam garantias de se achar um mínimo global.

Um dos modelos mais populares para vários problemas é o modelo de Redes Neurais (AGGARWAL et al., 2018). Neste modelo, temos camadas de "neurônios", os quais são representados por uma função de ativação de acordo com suas entradas. Na Figura 1.6, é ilustrado um exemplo de rede neural do tipo perceptron de múltiplas camadas com uma camada de entrada, a qual recebe características da amostra, uma camada oculta, a qual aproxima a função de erro, e uma camada de saída, a qual providencia um valor de predição. Neste exemplo, a rede neural é completamente conectada, onde cada neurônio representa uma soma  $\sum (peso[k]*entrada[k])$ , onde os valores de entrada vem da camada anterior, e os valores de peso são os parâmetros retidos no neurônio. Portanto, a representação do modelo é a matriz de neurônios e seus parâmetros.

Para atualizar os pesos (parâmetros) de uma rede neural, normalmente utiliza-se o algoritmo de retro-propagação (*Backpropagation*) (GOMEZ et al., 2017). No conjunto de benchmarks Rodinia (CHE et al., 2009), há um exemplo de rede neural onde é possível observar a implementação de *Backpropagation*. Abaixo, podemos observar a função de treino:

```

1 void bpnn_adjust_weights(delta, ndelta, ly, nly, w, oldw)

2 float *delta, *ly, **w, **oldw;

3 {

4  float new_dw;

```

```

5

int k, j;

6

ly[0] = 1.0;

7

//eta = 0.3;

8

//momentum = 0.3;

9

10 #ifdef OPEN

//omp_set_num_threads(NUM_THREAD);

11

12

#pragma omp parallel for \

13

shared(oldw, w, delta) \

14

private(j, k, new dw) \

15

firstprivate(ndelta, nly)

16 #endif

17

for (j = 1; j <= ndelta; j++) {</pre>

18

for (k = 0; k \le nly; k++) {

19

new_dw = ((ETA * delta[j] * ly[k]) + (MOMENTUM *

oldw[k][j]));

20

w[k][j] += new_dw;

21

oldw[k][j] = new_dw;

22

}

23

}

24 }

```

A função recebe delta (o vetor com os erros da próxima camada), ndelta (o tamanho deste vetor), ly (o vetor com os valores atuais de ativação), nly (o tamanho deste vetor), w (o novo vetor de pesos a ser criado), e oldw (que retém o vetor de pesos anterior). Cada peso é atualizado de acordo com a fórmula ETA \* delta[j] \* ly[k]) + (MOMENTUM \* oldw[k][j]), onde ETA e MOMENTUM são constantes para controlar a velocidade de treino e agressividade de adaptação dos parâmetros. Assim, esta pequena função é chave no funcionamento de redes neurais, e arquiteturas atuais propõe otimizações agressivas para melhorar sua performance. Neste minicurso, utilizamos a implementação do *Backpropagation* acima para ilustrar como podemos explorar a informação obtida por contadores de hardware e ferramentas de *profiling* para se obter desempenho em diversas arquiteturas, notadamente a arquitetura de CPU Cascade Lake e a arquitetura vetorial SX-Aurora TSUBASA.

# 1.8. Otimizando o Backpropagation com *profiling* e contadores de hardware

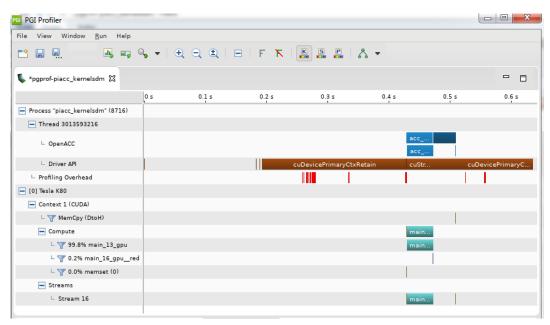

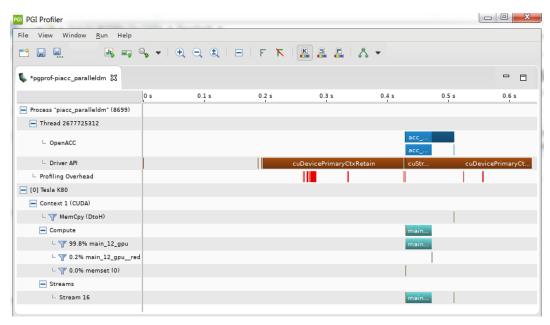

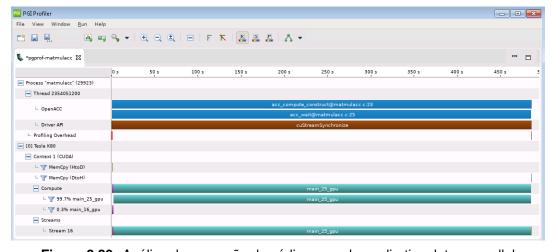

#### 1.8.1. NEC SX-Aurora

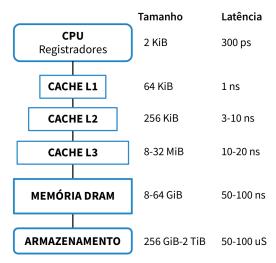

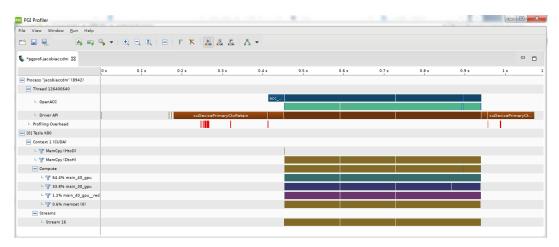

Analisando o código da aplicação através do trecho abaixo, juntamente com a análise da ftrace.out gerado pelo FTRACE observado na Figura 1.7, percebe-se que a função alloc\_1d\_dbl corresponde a 63,7% do tempo de execução. Ao analisar o código abaixo, observa-se que a mesma realiza a alocação dos pesos de forma tradicional, por meio de uma matriz bidimensional. No entanto, essa alocação não favorece o acesso aos dados por conta da falta de localidade espacial dos dados, o que sugere que a alocação de memória pode ser otimizada para uma alocação de memória contígua. Modificar a alocação dos dados gera a necessidade de se alterar várias outras regiões do código, uma

|            |                            | *            |                  |                  |              |               |             |                |                |                |         |                                            |

|------------|----------------------------|--------------|------------------|------------------|--------------|---------------|-------------|----------------|----------------|----------------|---------|--------------------------------------------|

|            | NALYSIS LIS                |              |                  |                  |              |               |             |                |                |                |         |                                            |

|            |                            | *            |                  |                  |              |               |             |                |                |                |         |                                            |

| ecution (  | Date : Sun                 | Mar 2        | 8 08:41:41       | 2021 -03         |              |               |             |                |                |                |         |                                            |

|            |                            |              | 48 (154.848      |                  |              |               |             |                |                |                |         |                                            |

|            |                            |              |                  |                  |              |               |             |                |                |                |         |                                            |

| VECUTTON : | TERMINATER                 | DIIT N       | OT IN MAIN H     | DDUCEUIDE        |              |               |             |                |                |                |         |                                            |

| ALCOTION   | TENTINATED                 | DO1 18       | JI IN HAIN       | NOCEDONE         |              |               |             |                |                |                |         |                                            |

| STOPPED /  |                            |              |                  |                  |              |               |             |                |                |                |         |                                            |

| CALLED FRO | OM main                    |              |                  |                  |              |               |             |                |                |                |         |                                            |

|            |                            |              |                  |                  |              |               |             |                |                |                |         |                                            |

| REQUENCY   | EXCLUSIVE                  |              | AVER.TIME        | MOPS             | MFLOPS       | V.OP          |             |                |                |                |         | PROC.NAME                                  |

|            | TIME[sec](                 | %)           | [msec]           |                  |              | RATIO         | V.LEN       | TIME           | MISS           | CONF           | HIT E.% |                                            |

| 34217738   | 98.697(                    | 63.7)        | 0.001            | 753.4            | 0.0          | 0.00          | 0.0         | 0.000          | 23.827         | 0.000          | 0.00    | alloc_1d_dbl                               |

| 1          |                            |              | 36506.441        | 744.5            | 0.0          | 0.00          | 0.0         | 0.000          | 8.087          | 0.000          |         | bpnn_free                                  |

| 4          | 13.218(                    | 8.5)         | 3304.383         | 2853.4           | 0.0          | 0.00          | 0.0         | 0.000          | 0.000          | 0.000          | 0.00    | alloc_2d_dbl                               |

| 1          | 5.524(                     | 3.6)         | 5524.487         | 400.6            | 3.0          | 0.00          | 0.0         | 0.000          | 0.000          | 0.000          |         | load                                       |

| 1          | 0.636(                     | 0.4)         | 636.077          | 3376.2           | 0.0          | 0.00          | 0.0         | 0.000          | 0.005          | 0.000          |         | bpnn_read                                  |

| 2<br>16    | 0.262(<br>0.004(           | 0.2)         | 131.075<br>0.267 | 2879.9<br>531.9  | 0.0          | 17.78         | 1.0         | 0.262<br>0.000 | 0.000          | 0.000<br>0.000 |         | bpnn_zero_weights                          |

| 2          | 0.004(                     | 0.0)         | 1.415            | 541.5            | 0.0<br>0.0   | 0.01          | 1.0<br>1.0  | 0.000          | 0.000          | 0.000          | 83.33   | <pre>bpnn_layerforward\$1   -thread0</pre> |

| 2          | 0.000(                     | 0.0)         | 0.058            | 488.4            | 0.1          | 0.03          | 1.0         | 0.000          | 0.000          | 0.000          | 100.00  |                                            |

| 2          | 0.000(                     | 0.0)         | 0.138            | 520.0            | 0.0          | 0.01          | 1.0         | 0.000          | 0.000          | 0.000          | 100.00  |                                            |

| 2          | 0.000(                     | 0.0)         | 0.068            | 512.5            | 0.1          | 0.02          | 1.0         | 0.000          | 0.000          | 0.000          | 100.00  |                                            |

| 2          | 0.000(                     | 0.0)         | 0.014            | 264.7            | 0.3          | 0.22          | 1.0         | 0.000          | 0.000          | 0.000          | 100.00  | -thread4                                   |

| 2          | 0.001(                     | 0.0)         | 0.288            | 528.3            | 0.0          | 0.01          | 1.0         | 0.000          | 0.000          | 0.000          | 100.00  |                                            |

| 2          | 0.000(                     | 0.0)         | 0.061            | 499.3            | 0.1          | 0.03          | 1.0         | 0.000          | 0.000          | 0.000          | 100.00  |                                            |

| 2<br>16    | 0.000(<br>0.000(           | 0.0)         | 0.090<br>0.005   | 516.1<br>335.9   | 0.0<br>5.4   | 0.02          | 1.0<br>0.0  | 0.000          | 0.000          | 0.000<br>0.000 | 66.67   | -thread7<br>squash                         |

| 2          | 0.000(                     | 0.0)         | 0.005            | 326.1            | 5.4          | 0.00          | 0.0         | 0.000          | 0.000          | 0.000          | 0.00    |                                            |

| 2          | 0.000(                     | 0.0)         | 0.005            | 331.2            | 5.4          | 0.00          | 0.0         | 0.000          | 0.000          | 0.000          | 0.00    |                                            |

| 2          | 0.000(                     | 0.0)         | 0.005            | 337.2            | 5.4          | 0.00          | 0.0         | 0.000          | 0.000          | 0.000          | 0.00    |                                            |

| 2          | 0.000(                     | 0.0)         | 0.005            | 332.2            | 5.3          | 0.00          | 0.0         | 0.000          | 0.000          | 0.000          | 0.00    |                                            |

| 2          | 0.000(                     | 0.0)         | 0.005            | 339.0            | 5.4          | 0.00          | 0.0         | 0.000          | 0.000          | 0.000          | 0.00    |                                            |

| 2          | 0.000(                     | 0.0)         | 0.005            | 336.7            | 5.4          | 0.00          | 0.0         | 0.000          | 0.000          | 0.000          | 0.00    |                                            |

| 2          | 0.000(                     | 0.0)         | 0.005            | 343.9            | 5.5          | 0.00          | 0.0         | 0.000          | 0.000          | 0.000          | 0.00    |                                            |

| 2<br>1     | 0.000(<br>0.000(           | 0.0)         | 0.005<br>0.052   | 341.0<br>628.4   | 5.4<br>0.0   | 0.00          | 0.0<br>0.0  | 0.000          | 0.000<br>0.000 | 0.000<br>0.000 | 0.00    | -thread7<br>bpnn_initialize                |

| 1          | 0.000(                     | 0.0)         | 0.032            | 141.1            | 0.0          | 0.00          | 0.0         | 0.000          | 0.000          | 0.000          |         | backprop_face                              |

| 1          | 0.000(                     | 0.0)         | 0.042            | 361.3            | 0.0          | 0.00          | 0.0         | 0.000          | 0.000          | 0.000          |         | setup                                      |

| 16         | 0.000(                     | 0.0)         | 0.002            | 597.1            | 2.9          | 1.72          | 1.0         | 0.000          | 0.000          | 0.000          |         | bpnn_adjust_weights\$1                     |

| 2          | 0.000(                     | 0.0)         | 0.002            | 574.2            | 2.3          | 1.42          | 1.0         | 0.000          | 0.000          | 0.000          | 100.00  |                                            |

| 2          | 0.000(                     | 0.0)         | 0.002            | 584.5            | 3.2          | 1.96          | 1.0         | 0.000          | 0.000          | 0.000          | 100.00  |                                            |

| 2          | 0.000(                     | 0.0)         | 0.002            | 602.7            | 3.1          | 1.86          | 1.0         | 0.000          | 0.000          | 0.000          | 100.00  |                                            |

| 2<br>2     | 0.000(<br>0.000(           | 0.0)<br>0.0) | 0.002<br>0.002   | 607.9<br>589.3   | 3.1<br>2.8   | 1.82<br>1.73  | 1.0<br>1.0  | 0.000<br>0.000 | 0.000          | 0.000<br>0.000 | 100.00  |                                            |

| 2          | 0.000(                     | 0.0)         | 0.002            | 596.6            | 2.8          | 1.68          | 1.0         | 0.000          | 0.000          | 0.000          | 100.00  |                                            |

| 2          | 0.000(                     | 0.0)         | 0.002            | 622.5            | 3.0          | 1.75          | 1.0         | 0.000          | 0.000          | 0.000          | 100.00  |                                            |

| 2          | 0.000(                     | 0.0)         | 0.002            | 606.8            | 2.8          | 1.68          | 1.0         | 0.000          | 0.000          | 0.000          | 100.00  |                                            |

| 2          | 0.000(                     | 0.0)         | 0.009            | 322.5            | 0.0          | 0.00          | 0.0         | 0.000          | 0.000          |                |         | bpnn_layerforward                          |

| 1          | 0.000(                     | 0.0)         | 0.013            | 503.1            | 0.0          | 0.00          | 0.0         | 0.000          | 0.000          | 0.000          |         | bpnn_internal_create                       |

| 1<br>2     | 0.000(                     | 0.0)         | 0.011            | 304.0            | 0.0          | 0.00          | 0.0         | 0.000          | 0.000          | 0.000          |         | bpnn_train_kernel                          |

|            | 0.000(                     | 0.0)         | 0.002<br>0.001   | 730.0<br>281.2   | 0.0<br>0.0   | 0.00          | 0.0<br>0.0  | 0.000<br>0.000 | 0.000          | 0.000<br>0.000 |         | bpnn_adjust_weights<br>main                |

|            |                            |              | 0.001            | 201.2            | 0.0          |               | 0.0         |                |                |                |         |                                            |

| 1          | 0.000(                     |              | 0.000            | 1441.9           | 292.0        | 49.19         | 16.0        | 0.000          | 0.000          | 0.000          | 5000    | bonn output error                          |

|            | 0.000(<br>0.000(<br>0.000( | 0.0)         | 0.000<br>0.000   | 1441.9<br>2461.5 | 292.0<br>0.0 | 49.19<br>0.00 | 16.0<br>0.0 | 0.000<br>0.000 | 0.000          | 0.000<br>0.000 |         | bpnn_output_error<br>bpnn_hidden_error     |

Figura 1.7. Resultados do comando FTRACE para a versão original do *Backpropagation*.

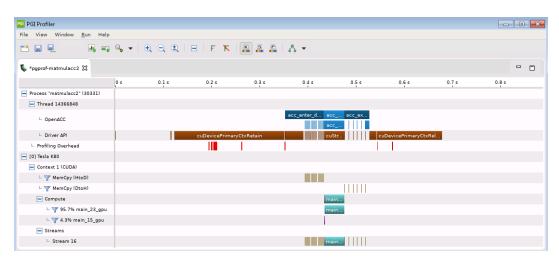

vez que a forma de acesso e indexação dos dados agora deve ser feita de forma diferente. Dessa forma, o código abaixo é modificado de modo a substituir a alocação de uma matriz de tamanho  $m \times n$  por uma alocação de um espaço contíguo de memória de tamanho  $m \times n$ .

```

1 BPNN *bpnn internal create(n in, n hidden, n out)

2 int n_in, n_hidden, n_out;

3 {

4

. . .

5

6 newnet->input weights = alloc 2d dbl(n in + 1, n hidden

newnet->hidden weights = alloc 2d dbl(n hidden + 1,

n_out + 1);

8

9

newnet->input_prev_weights = alloc_2d_dbl(n_in + 1,

n_hidden + 1);

10

newnet->hidden_prev_weights = alloc_2d_dbl(n_hidden +

1, n_out + 1);

11

12

return (newnet);

13 }

```

A otimização é apresentada nos trechos de código abaixo. Na linha 2 do primeiro bloco, adicionamos long unsigned na declaração da variável, e das linha 8 à 12 substitui-se a função de alocação bidimensional pela função de alocação unidimensional contígua.

```

1 BPNN *bpnn_internal_create(n_in, n_hidden, n_out)

2 long unsigned int n_in, n_hidden, n_out;

3 {

4

. . .

5

6

newnet->input weights = alloc 1d dbl((n in + 1) * (

n_hidden + 1));

7

newnet->hidden_weights = alloc_1d_dbl((n_hidden + 1) *

(n_out + 1));

8

9

newnet->input_prev_weights = alloc_1d_dbl((n_in + 1) *

(n_hidden + 1));

10

newnet->hidden_prev_weights = alloc_1d_dbl((n_hidden +

1) * (n out + 1));

11

12

return (newnet);

13 }

```

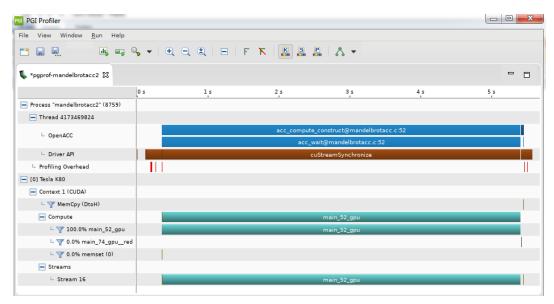

|                                                                                            | NALYSIS LIS      |        |                    |                    |                    |                |              |                |         |          |                |                                          |

|--------------------------------------------------------------------------------------------|------------------|--------|--------------------|--------------------|--------------------|----------------|--------------|----------------|---------|----------|----------------|------------------------------------------|

|                                                                                            |                  |        |                    |                    |                    |                |              |                |         |          |                |                                          |

|                                                                                            |                  |        |                    |                    |                    |                |              |                |         |          |                |                                          |

| Execution Date : Sun Mar 28 04:56:48 2021 -03<br>Fotal CPU Time : 0:00'09"394 (9.394 sec.) |                  |        |                    |                    |                    |                |              |                |         |          |                |                                          |

| lotal CPU                                                                                  | Time : 0:00      | 0.05.3 | 94 (9.394 s        | ec.)               |                    |                |              |                |         |          |                |                                          |

|                                                                                            |                  |        |                    |                    |                    |                |              |                |         |          |                |                                          |

| EXECUTION 1                                                                                | TERMINATED       | BUT N  | OT IN MAIN         | PROCEDURE          |                    |                |              |                |         |          |                |                                          |

|                                                                                            |                  |        |                    |                    |                    |                |              |                |         |          |                |                                          |

| STOPPED /                                                                                  |                  |        |                    |                    |                    |                |              |                |         |          |                |                                          |

| CALLED FRO                                                                                 | OM main          |        |                    |                    |                    |                |              |                |         |          |                |                                          |

|                                                                                            |                  |        |                    |                    |                    |                |              |                |         |          |                |                                          |

| FREQUENCY                                                                                  | EXCLUSIVE        |        | AVER.TIME          | MOPS               | MFLOPS             | V.OP           | AVER.        | VECTOR         | L1CACHE | CPU PORT | VLD LLC        | PROC.NAME                                |

|                                                                                            | TIME[sec](       | ( % )  | [msec]             |                    |                    | RATIO          |              | TIME           | MISS    |          | HIT E.%        |                                          |

|                                                                                            |                  |        |                    |                    |                    |                |              |                |         |          |                |                                          |

| 1                                                                                          | 6.578(           |        | 6577.831           | 2611.8             | 0.0                |                | 138.5        | 0.000          | 0.263   | 0.000    |                | bpnn_read                                |

| 16                                                                                         | 1.638(           |        | 102.395            | 10404.4            | 2662.5             | 75.59          | 16.0         | 1.638          | 0.000   | 0.000    |                | bpnn_adjust_weights\$1                   |

| 2                                                                                          | 0.205(           | 2.2)   | 102.396            | 10404.3            | 2662.5             | 75.59          | 16.0         | 0.205          | 0.000   | 0.000    | 33.35          | -thread0                                 |

| 2                                                                                          | 0.205(           | 2.2)   | 102.395            | 10404.4            | 2662.5             | 75.59          | 16.0         | 0.205          | 0.000   | 0.000    | 33.35          | -thread1                                 |

| 2<br>2                                                                                     | 0.205(<br>0.205( | 2.2)   | 102.395<br>102.395 | 10404.4<br>10404.4 | 2662.5<br>2662.5   | 75.59<br>75.59 | 16.0<br>16.0 | 0.205<br>0.205 | 0.000   | 0.000    | 33.35<br>33.35 | -thread2<br>-thread3                     |

| 2                                                                                          | 0.205(           | 2.2)   | 102.395            | 10404.4            | 2662.5             | 75.59          | 16.0         | 0.205          | 0.000   | 0.000    | 33.35          | -thread4                                 |

| 2                                                                                          | 0.205(           | 2.2)   | 102.395            | 10404.4            | 2662.5             | 75.59          | 16.0         | 0.205          | 0.000   | 0.000    | 33.35          | -thread5                                 |

| 2                                                                                          | 0.205(           | 2.2)   | 102.395            | 10404.4            | 2662.5             | 75.59          | 16.0         | 0.205          | 0.000   | 0.000    | 33.35          | -thread6                                 |

| 2                                                                                          | 0.205(           | 2.2)   | 102.395            | 10404.4            | 2662.5             | 75.59          | 16.0         | 0.205          | 0.000   | 0.000    | 33.35          | -thread7                                 |

| 2                                                                                          | 1.025(           |        | 512.373            | 5042.6             | 0.0                | 44.16          |              | 1.025          | 0.000   | 0.000    |                | bpnn_zero_weights                        |

| 16                                                                                         | 0.152(           | 1.6)   | 9.528              | 28483.8            | 14086.6            | 98.91          | 256.0        | 0.150          | 0.000   | 0.000    | 69.87          | bpnn_layerforward\$1                     |

| 2                                                                                          | 0.020(           | 0.2)   | 10.052             | 27026.0            | 13351.7            | 98.81          |              | 0.019          | 0.000   | 0.000    | 2.92           | -thread0                                 |

| 2                                                                                          | 0.019(           | 0.2)   | 9.502              | 28559.4            | 14124.7            | 98.91          |              | 0.019          | 0.000   | 0.000    | 98.88          | -thread1                                 |

| 2                                                                                          | 0.019(           | 0.2)   | 9.426              | 28787.5            | 14239.7            | 98.93          |              | 0.019          | 0.000   | 0.000    | 26.30          | -thread2                                 |

| 2                                                                                          | 0.019(           | 0.2)   | 9.400              | 28865.9            | 14279.2<br>14204.6 | 98.94          |              | 0.019          | 0.000   | 0.000    | 99.98<br>49.33 | -thread3                                 |

| 2<br>2                                                                                     | 0.019(<br>0.019( | 0.2)   | 9.449<br>9.587     | 28717.9<br>28312.9 | 14204.6            | 98.93<br>98.90 |              | 0.019<br>0.019 | 0.000   | 0.000    | 99.34          | -thread4<br>-thread5                     |

| 2                                                                                          | 0.019(           | 0.2)   | 9.406              | 28846.3            | 14269.4            | 98.93          |              | 0.019          | 0.000   | 0.000    | 82.35          | -thread6                                 |

| 2                                                                                          | 0.019(           | 0.2)   | 9.403              | 28856.0            | 14274.3            | 98.93          |              | 0.019          | 0.000   | 0.000    | 99.82          | -thread7                                 |

| 17                                                                                         | 0.000(           | 0.0)   | 0.007              | 248.2              | 4.1                | 0.00           | 0.0          | 0.000          | 0.000   | 0.000    |                | squash                                   |

| 3                                                                                          | 0.000(           | 0.0)   | 0.005              | 239.4              | 5.2                | 0.00           | 0.0          | 0.000          | 0.000   | 0.000    | 0.00           | -thread0                                 |

| 2                                                                                          | 0.000(           | 0.0)   | 0.007              | 241.4              | 3.8                | 0.00           | 0.0          | 0.000          | 0.000   | 0.000    | 0.00           | -thread1                                 |

| 2                                                                                          | 0.000(           | 0.0)   | 0.007              | 246.0              | 3.9                | 0.00           | 0.0          | 0.000          | 0.000   | 0.000    | 0.00           | -thread2                                 |

| 2                                                                                          | 0.000(           | 0.0)   | 0.007              | 247.4              | 3.9                | 0.00           | 0.0          | 0.000          | 0.000   | 0.000    | 0.00           | -thread3                                 |

| 2                                                                                          | 0.000(           | 0.0)   | 0.007              | 248.5              | 3.9                | 0.00           | 0.0          | 0.000          | 0.000   | 0.000    | 0.00           | -thread4                                 |

| 2<br>2                                                                                     | 0.000(           | 0.0)   | 0.007              | 253.0              | 4.0                | 0.00           | 0.0          | 0.000          | 0.000   | 0.000    | 0.00           | -thread5<br>-thread6                     |

| 2                                                                                          | 0.000(<br>0.000( | 0.0)   | 0.007<br>0.007     | 252.1<br>259.4     | 3.9<br>4.0         | 0.00           | 0.0<br>0.0   | 0.000          | 0.000   | 0.000    | 0.00           | - thread7                                |

| 1                                                                                          | 0.000(           | 0.0)   | 0.052              | 641.0              | 0.0                | 0.00           | 0.0          | 0.000          | 0.000   | 0.000    |                | bpnn_initialize                          |

| 1                                                                                          | 0.000(           | 0.0)   | 0.042              | 374.2              | 0.0                | 0.00           | 0.0          | 0.000          | 0.000   | 0.000    |                | setup                                    |

| 1                                                                                          | 0.000(           | 0.0)   | 0.038              | 150.1              | 0.0                | 0.00           | 0.0          | 0.000          | 0.000   | 0.000    |                | backprop_face                            |

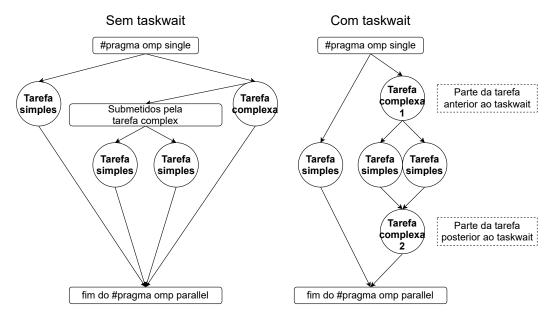

| 10                                                                                         | 0.000(           | 0.0)   | 0.002              | 285.5              | 0.0                | 0.00           | 0.0          | 0.000          | 0.000   | 0.000    |                | alloc_1d_dbl                             |